iTESS is a full custom memory compiler capable of generating end layout, LEF, Verilog and schematic views. The ease of use of this tool makes it seamlessly usable by layout, CAD or circuit designers. When used along with iTIME it can generate memory level timing and margin results.

![]()

Features

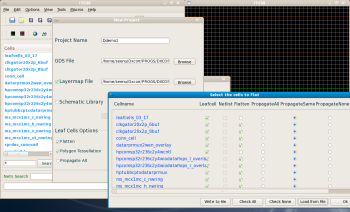

iTESS is a full featured memory compiler. iTESS accepts the following inputs

iTESS is a full featured memory compiler. iTESS accepts the following inputs

- GDS of leaf cells

- Netlists of leaf cells

- Verilog of leaf cells (optional)

- Technology layermap

iTESS generates the following views once layout tessellation is completed

- GDS stream of the resultant Memory structure

- Structural and behavioral verilog

- Spice netlist

- Metal fill

- Power grid completion and power fill

- LEF and abstract views

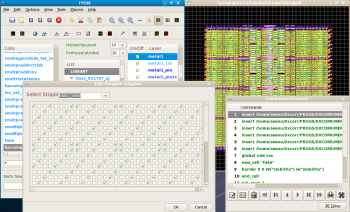

In a full custom environment, layout tessellation is achieved by using GULT language to tile the leaf cells to form end layout. +Interactive coding with no training requirement

iTESS is a full featured memory compiler. iTESS accepts the following inputs

In a semi custom environment, inbuilt templates for numerous architectures and floor plans can be used for tessellation. Some of the pre-built templates included with iTESS are

iTESS is a full featured memory compiler. iTESS accepts the following inputs

In a semi custom environment, inbuilt templates for numerous architectures and floor plans can be used for tessellation. Some of the pre-built templates included with iTESS are

+High Performance SRAM memory templates

+High Density SRAM memory templates

+'X' port Register file memory templates Ex. 1r1w, 2r5w etc

+CAMs, CAM-RAM structures

+In conjunction with iTIME and iCHAR, “what if” architectural feasibility studies and preplanning for power, performance and density targets.

+Guide to select optimal architecture which is aware of well proximity effects and process limitations

iTESS is unique in its class for the following reasons

iTESS is unique in its class for the following reasons

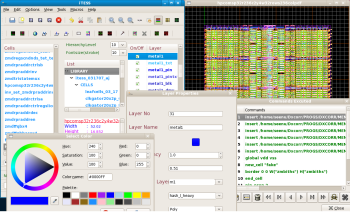

+It recognizes the layout connectivity at run time.

+The resulting netlist and verilog reflect all the connectivity of the layout, thus avoiding user input for connectivity.

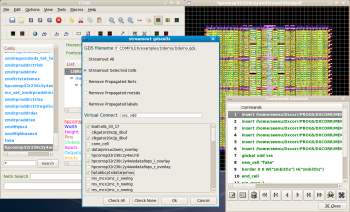

+Automatic pin propagation

+Automatic net propagation

+Layout created with instance names

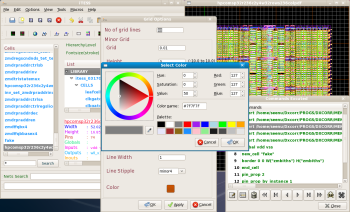

+Parametrized polygon drawing ability.

+Very user friendly interface, requiring no layout expertise.

+Highly multi threaded for optimal performance.

+Point to point router included.