Features

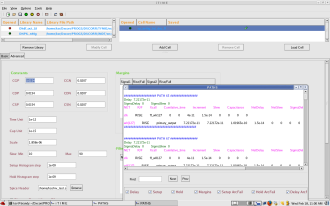

- Cell based statistical static timing analysis tool

- Self timed design margin computation and identification including statistical variations

- Handles special circuits and bidirectional memory structures (like precharge, column multiplexers, low swing sense amplifiers etc.)

- MIN and MAX timing based on iCHAR cell characterization

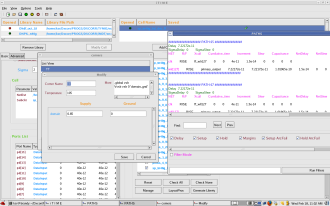

- Slack report generation and graphical analysis engine

- Mean, sigma and variance of critical paths

- Accurate and reliable analysis

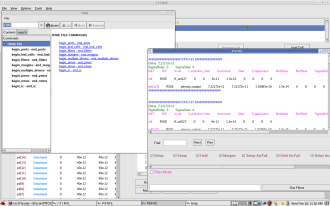

- Critical path spice level netlist generation with sensitization

- Selective spicing of some of the critical paths on demand

- Fast computation through efficient distribution algorithm

- For modern technologies transistor characteristics vary 15% to 25% based on the well proximity effect ( WPE ) and layout proximity effects( LPE ) alone. iTIME gives accurate results by using the appropriate timing information for each leaf cell instance based on its unique proximity.

- Generates industry standard plug'n play timing views for seamless integration at the chip level while giving accurate timing number for every bit.

- Generates power views.

- Special internal extensions for low swing memory specific circuits

- no manual Critical path based simulation needed to verify timing and margins. In case of doubt, you can use the pruned netlists generated for every critical path.

- Highly multi-threaded software to maximum usage of machine time.

- Internal paths of memory are analyzed and slack is reported.

- Statistical analysis of ALL paths facilitates predicting the 'yield curve' and speed binning of N number of parts.

- Power views.